# **NEXSYS®** Component Technology

## **NEXSYS®** Components

For VIVISUN Advanced Lighted Pushbutton Switches and Indicators, NEXSYS Modules, and NEXSYS Thru-Hole Devices (THD).

**ARINC 429 Signal Converters**

**Defined Logic**

**Solid State Relay**

**Electronic Latch**

**Electronic Rotary**

Pulse/Timer

**Time Delay**

**Square Wave Oscillator**

**Voltage Sensor**

**Current Sensor**

**Diode Pack**

**Terminal Block**

**NEXSYS® Module and Configurations**

**VIVISUN® Body Configurations**

**NEXSYS®** Thru-Hole Devices

| Document Type   | Technical Guide |

|-----------------|-----------------|

| Document Number | TG-NCT-21       |

| Revision        | D               |

## **Document Overview**

The purpose of this document is to provide complete technical information on NEXSYS components, NEXSYS Module, internal component configurations, and NEXSYS Thru-Hole Devices manufactured by Applied Avionics.

Please ensure you are viewing the most current revision of this document by visiting:

• https://appliedavionics.com/techguides/

For technical support or customer service questions, please contact us via:

• Phone: 1-888-848-4786, or

• Email: support@appliedavionics.com, or

• Online: https://www.appliedavionics.com/contact-us/

| Document Revision History (last 5 revisions shown) |                |             |                                                                                                                                                                                                                                                                                                                     |  |  |

|----------------------------------------------------|----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision                                           | Effective Date | Approved By | Description                                                                                                                                                                                                                                                                                                         |  |  |

|                                                    | 02/01/2022     | LKJ         | Initial Release                                                                                                                                                                                                                                                                                                     |  |  |

| А                                                  | 04/23/2024     | LKJ         | Added MPTB data, SSR3 Data, On-State Resistance Operating Parameter updates on ARINC Converters, DL, SSR, EL, ER, SWO. VS, and CS, Propagation Input Timing Operating Parameter update on DL, added RF Conducted Susceptibility Electrical Qualifications for SSR3, changed 22-006 to 22-026, added /116, /117 info |  |  |

| В                                                  | 09/10/2024     | МН          | Corrected Category for Electrostatic Discharge row in Appendix A Table A.2                                                                                                                                                                                                                                          |  |  |

| С                                                  | 10/08/2024     | KL          | Removed Parity paragraph from Section 2.1.1, added more Power Input Aircraft Power qualifications to table A.2 Electrical Qualifications                                                                                                                                                                            |  |  |

|                                                    |                |             |                                                                                                                                                                                                                                                                                                                     |  |  |

# **Table of Contents**

| 1.0 NEXSYS® Component Technology – Overview                  | 1  |

|--------------------------------------------------------------|----|

| 2.0 NEXSYS® Components                                       | 3  |

| 2.1 Data Conversion Components                               | 5  |

| 2.1.1 ARINC 429 Signal Converters                            | 6  |

| 2.1.1.1 ARINC 429 Single-Bit Converter (SR429/1M)            | 9  |

| 2.1.1.2 ARINC 429 Multi-Bit Converter (SR429/4M)             | 10 |

| 2.1.1.3 ARINC 429 Multi-Bit Decoding Converter (SR429/4D)    | 12 |

| 2.1.1.4 ARINC 429 Signal Converters, Operating Parameters    | 15 |

| 2.1.2 RS232/RS422 Transceiver Module                         | 16 |

| 2.1.2.1 RS232/RS422 Transceiver Module, Operating Parameters | 18 |

| 2.2 Signal Switching/Control Components                      | 19 |

| 2.2.1 Defined Logic                                          | 20 |

| 2.2.1.1 Defined Logic 1 (DL1)                                | 22 |

| 2.2.1.2 Defined Logic 2 (DL2)                                | 24 |

| 2.2.1.3 Defined Logic 3 (DL3)                                | 27 |

| 2.2.1.4 Defined Logic 4 (DL4)                                | 30 |

| 2.2.1.5 Defined Logic, Operating Parameters                  | 33 |

| 2.2.2 Solid State Relay                                      | 34 |

| 2.2.2.1 Single (SSR)                                         | 35 |

| 2.2.2.2 Combination (SSRC)                                   | 37 |

| 2.2.2.3 Solid State Relay, Operating Parameters              | 41 |

| 2.3 State Control Components                                 | 42 |

| 2.3.1 Electronic Latch                                       | 43 |

| 2.3.1.1 Electronic Latch, Operating Parameters               | 46 |

| 2.3.2 Electronic Rotary                                      | 47 |

| 2.3.2.1 Electronic Rotary, Operating Parameters              | 49 |

| 2.4 Timing Components                                        | 50 |

| 2.4.1 Pulse/Timer                                            | 51 |

| 2.4.1.1 Pulse/Timer, Operating Parameters                    | 53 |

| 2.4.2 Time Delay                                             | 54 |

| 2.4.2.1 Time Delay, Operating Parameters                     | 57 |

| 2.4.3 Square Wave Oscillator                                 | 58 |

| 2.4.3.1 Square Wave Oscillator, Operating Parameters | 61 |

|------------------------------------------------------|----|

| 2.5 Sensing Components                               | 62 |

| 2.5.1 Voltage Sensor                                 | 63 |

| 2.5.1.1 Voltage Sensor, Operating Parameters         | 66 |

| 2.5.2 Current Sensor                                 | 67 |

| 2.5.2.1 Current Sensor, Operating Parameters         | 69 |

| 2.6 Passive Components                               | 70 |

| 2.6.1 Diode Pack                                     | 71 |

| 2.6.1.1 Diode Pack, Operating Parameters             | 72 |

| 2.6.2 Terminal Block                                 | 73 |

| 2.6.2.1 Terminal Block, Operating Parameters         | 76 |

| 3.0 NEXSYS® Module and Configurations                | 77 |

| 3.1 Component Configurations                         | 78 |

| 3.2 Termination                                      | 79 |

| 3.3 Installation and Mounting Options                | 80 |

| 4.0 VIVISUN® Body Configurations                     | 83 |

| 4.1 Component Configurations                         | 84 |

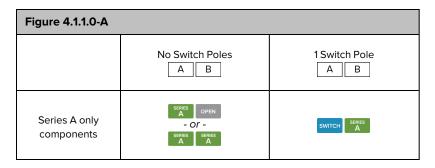

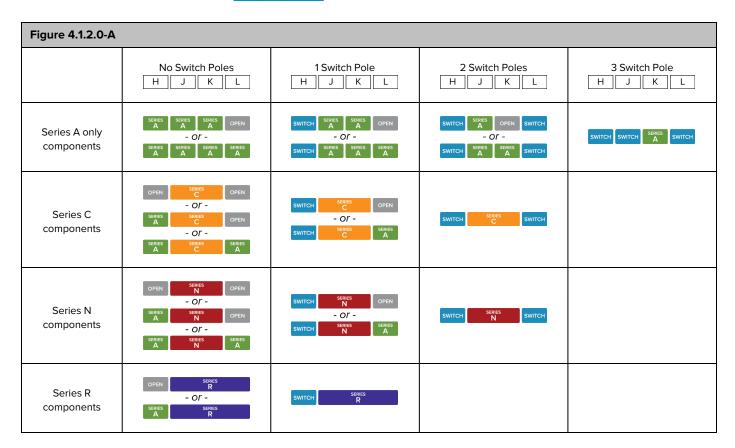

| 4.1.1 VIVISUN Compact Bodies                         | 84 |

| 4.1.2 VIVISUN High Capacity Bodies                   | 84 |

| 4.2 Termination                                      | 85 |

| 4.3 Installation                                     | 85 |

| 5.0 NEXSYS® Thru-hole Devices                        | 87 |

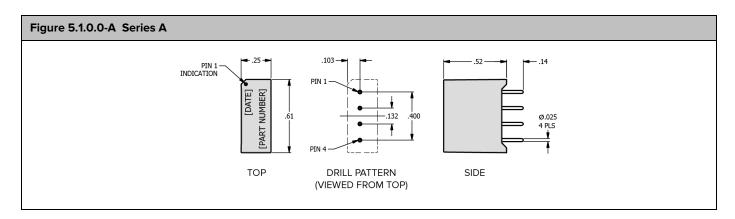

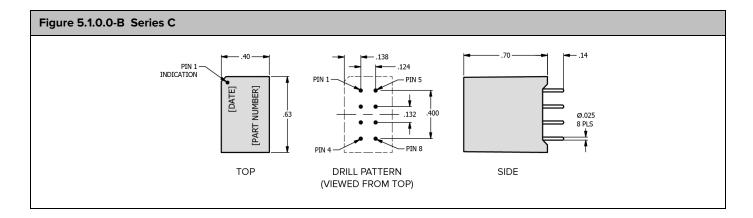

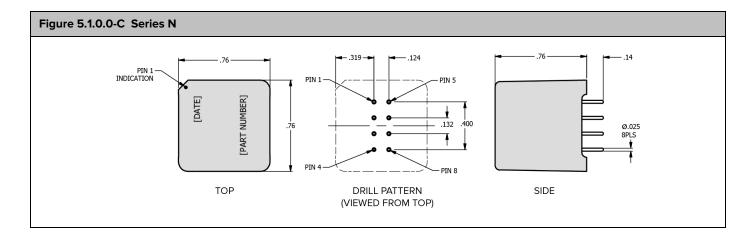

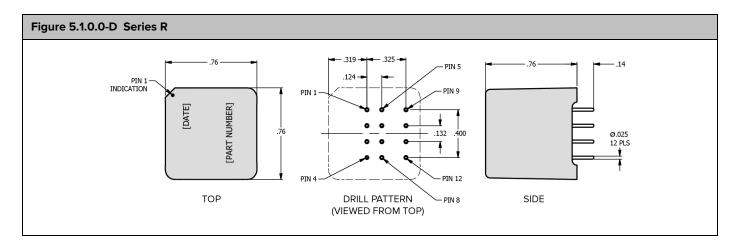

| 5.1 Dimensions and Pin Spacing                       | 88 |

| 5.2 Installation                                     | 89 |

| 6.0 Component Pinout                                 | 91 |

| Appendix A Qualification Tables                      | 95 |

| A.1 Environmental Qualifications                     | 95 |

| Δ 2 Flectrical Qualifications                        | 96 |

# 1.0 NEXSYS® Component Technology – Overview

NEXSYS Component Technology is a platform of solid-state and discrete electronic components used to create custom multi-function digital and analog control circuits. The form factor of <a href="NEXSYS">NEXSYS</a> Components allows them to be packaged inside VIVISUN switch and indicator bodies; see <a href="Section 4.0">Section 4.0</a>, inside NEXSYS Modules; see <a href="Section 3.0">Section 3.0</a>, or as a Thru-Hole Device; see <a href="Section 5.0">Section 5.0</a>. NEXSYS components can function independently or in combination with other NEXSYS components, electromechanical switches, and aircraft systems.

Applied Avionics has a dedicated <u>NEXSYS Application Development Team</u> to assist with design and implementation. NEXSYS application engineers can develop wiring diagrams, LTSpice® simulations, configure part numbers and help with troubleshooting. For questions and application assistance, contact a NEXSYS application engineer at 1-888-848-4786.

The Applied Avionics Part Configurator (https://configurator.appliedavionics.com/) makes it easy to configure a complete solution using NEXSYS Component Technology, including ready-to-order part numbers and specification of:

- · VIVISUN Switches and Indicators

- NEXSYS Component Options

- NEXSYS Modules and Thru-Hole Devices

- NEXSYS and VIVISUN Accessories (i.e., Connector Plug, Mounting Hardware)

This page intentionally left blank.

# 2.0 NEXSYS® Components

NEXSYS components are solid-state devices that contain no firmware or software and are designed, tested, and qualified to perform reliably in the most demanding military and commercial applications. NEXSYS components are packaged inside VIVISUN switches and indicators (Compact and High Capacity), NEXSYS Modules, and are available as Thru-Hole Devices. For specific performance characteristics, each NEXSYS component section includes parametric data.

#### **Component Performance**

The NEXSYS Components are commercial-off-the-shelf (COTS) items. This standard catalog hardware includes features to allow for flexible interface design solutions while also meeting aircraft performance standards. The NEXSYS Components are designed, tested, and qualified to MIL-PRF-22885/116, MIL-PRF-22885/117, DO-160 and MIL-STD-461 requirements. Specifications are available in our MIL-PRF and DO-160 Documents page, and the qualification table is available in Appendix A. Detailed test data is made available upon request.

### **Component Series**

Four (4) component series designations define the form factor and number of I/O pins: Series A, Series C, Series N, or Series R, see <u>Figure 2.0.0.0-A</u>. Component series also refers to functionality, configuration, and packaging options of NEXSYS components.

Figure 2.0.0.0-A

SERIES A

SERIES N

SERIES R

4 Pin 8 Pin 8 Pin 12 pin

#### **Component Configurations**

NEXSYS components are packaged inside VIVISUN switches and indicators (Compact and High Capacity), NEXSYS Modules, and are available as Thru-Hole Devices, see Figure 2.0.0.0-B.

- For NEXSYS Module packaging options, see Section 3.0.

- For VIVISUN switch and indicator packaging options, see Section 4.0.

- For NEXSYS Thru-Hole Device specifications, see Section 5.0.

| Figure 2.0.0.0-B |                                       |                                  |                                        |                                                  |  |  |  |

|------------------|---------------------------------------|----------------------------------|----------------------------------------|--------------------------------------------------|--|--|--|

|                  | NEXSYS<br>Module<br>(See <u>3.1</u> ) | VIVISUN Compact Body (See 4.1.1) | VIVISUN High Capacity Body (See 4.1.2) | NEXSYS<br>Thru-Hole Devices<br>(See <u>5.1</u> ) |  |  |  |

| SERIES A         | <b>✓</b>                              | <b>√</b>                         | /                                      | /                                                |  |  |  |

| SERIES C         | /                                     |                                  | 1                                      | 1                                                |  |  |  |

| SERIES N         | /                                     |                                  | /                                      | 1                                                |  |  |  |

| SERIES R         | /                                     |                                  | /                                      | 1                                                |  |  |  |

## **Component Functions and Series**

NEXSYS Components are categorized according to application function, and summarized in the table below.

| Figure 2.0.0.0-C            | Figure 2.0.0.0-C                                                                                                                                                                                                                                                                             |          |  |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

| Function                    | Description                                                                                                                                                                                                                                                                                  | Series   |  |  |  |  |

| Data Conversion             |                                                                                                                                                                                                                                                                                              |          |  |  |  |  |

| ARINC 429 Signal Converters | Autonomous ARINC 429 receivers with the protocol logic necessary to capture and convert a specified data-word to discrete output(s), controlled by the decode of a single label and bit, multiple-bits, or multi-bit Binary Decode (BD), see 2.1.1.                                          | SERIES R |  |  |  |  |

| Signal Switching/Control    |                                                                                                                                                                                                                                                                                              |          |  |  |  |  |

| Defined Logic               | Digital electronic device that performs Boolean logic gate operations AND, OR, NOT, NAND, NOR, XOR, XNOR, as well as BUFFER, see 2.2.1.                                                                                                                                                      | SERIES   |  |  |  |  |

| Solid State Relay           | Normally Open (NO) and Normally Closed (NC) solid-state relays available individually (SSR) or in a combination of four (SSRCH). The bidirectional inputs are polarity insensitive, and the device performs buffered switching with optical isolation between inputs and outputs, see 2.2.2. | SERIES A |  |  |  |  |

| State Control               |                                                                                                                                                                                                                                                                                              |          |  |  |  |  |

| Electronic Latch            | Electronic latching with multiple trigger modes to activate orthogonal switching (flip-flop) between two known states and a 1Hz blink output, see $\underline{2.3.1}$ .                                                                                                                      | SERIES   |  |  |  |  |

| Electronic Rotary           | Electronic rotary control that performs incremental switching through a loop of up to four latched output states, controlled by input level transitions, see $\underline{2.3.2}$ .                                                                                                           | SERIES C |  |  |  |  |

| Timing                      |                                                                                                                                                                                                                                                                                              |          |  |  |  |  |

| Pulse/Timer                 | Dual-channel edge detector and pulse generator with independent channels to perform stable retriggerable/resettable one-shot operation for fixed timing applications. Pulse-width output timing options range from 125 ms to 20 sec, see 2.4.1.                                              | SERIES C |  |  |  |  |

| Time Delay                  | Time-delay output, controlled by input triggers or power-up. Output timing options range from 125 ms to 4 hrs, see $\underline{2.4.2}$ .                                                                                                                                                     | SERIES A |  |  |  |  |

| Square Wave Oscillator      | Oscillating output controlled by input triggers or power-up. Frequency (cycles/sec) and Period (sec/cycle) options range from 0.25 Hz (4 sec) to 500 Hz (0.002 sec), see <u>2.4.3</u> .                                                                                                      | SERIES A |  |  |  |  |

| Sensing                     |                                                                                                                                                                                                                                                                                              |          |  |  |  |  |

| Voltage Sensor              | Direct Current (DC) voltage sensor performs undervoltage and overvoltage detection to trigger the output. Sensed-voltage (VSD1) setpoint options range from +1 to 48 VDC, and sensed-low voltage (VSD2) setpoint options range from 50 mVDC to 1000 mVDC (+1 VDC), see 2.5.1.                | SERIES A |  |  |  |  |

| Current Sensor              | Direct Current (DC), low-side current sensor that performs undercurrent and overcurrent detection to trigger the output. Sensed-current setpoint options range from 10 mA to 1000 mA (1.0 A), see $\underline{2.5.2}$ .                                                                      | SERIES A |  |  |  |  |

| Passive                     |                                                                                                                                                                                                                                                                                              |          |  |  |  |  |

| Diode Pack                  | Package of two diodes specified as either commercial (1N6484) or military (1N5621JANTX) grade, see <u>2.6.1</u> .                                                                                                                                                                            | SERIES A |  |  |  |  |

| Terminal Block              | 4-splice configuration for increased wiring efficiency, see <u>2.6.2</u> .                                                                                                                                                                                                                   | SERIES A |  |  |  |  |

# 2.1 Data Conversion Components

Components that interface with system serial buses and convert data from one format to another.

Data Conversion components include:

- ARINC 429 Signal Converters

- RS232/RS422 Transceiver Module

## 2.1.1 ARINC 429 Signal Converters

## **Summary Description**

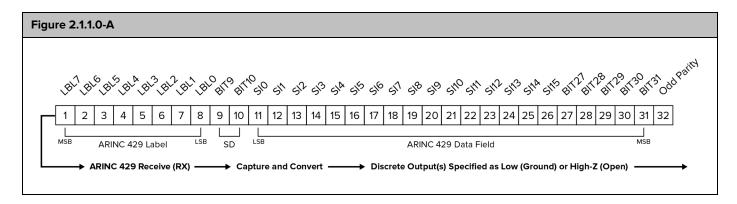

The NEXSYS ARINC 429 Signal Converter is either a Series N (8 Pin) or Series R (12 Pin) autonomous ARINC 429 receiver that includes the protocol logic necessary to capture and decode an ARINC 429 data word. The 32-bit data word is then converted into a discrete output, see <u>Figure 2.1.1.0-A</u>. Some configurations are also capable of performing interface solutions for encoding applications by performing the multi-bit decode operation.

The NEXSYS Signal Converter is available in three configuration types based on the requirements for data conversion and output control:

- Single-Bit Converter (SR429/1M), see Section 2.1.1.1

- Multi-Bit Converter (SR429/4M), see Section 2.1.1.2

- Multi-Bit Decoding Converter (SR429/4D), see <u>Section 2.1.1.3</u>

The simple input-pin interface does not rely on any microcontroller, software or firmware control, eliminating the qualification requirements of DO-178 or complex hardware (DO-254).

The NEXSYS ARINC 429 Signal Converter (SR429/1M, /4M, /4D) is a commercial-off-the-shelf (COTS) item. This standard catalog hardware includes features to allow for flexible interface design solutions while also meeting aircraft performance standards. The SR429 is designed, tested, and qualified to MIL-PRF-22885/116, MIL-PRF-22885/117, DO-160 and MIL-STD-461 requirements. Specifications are available in our MIL-PRF and DO-160 Documents page, and the qualification table is available in Appendix A.

## **Standard Input Characteristics**

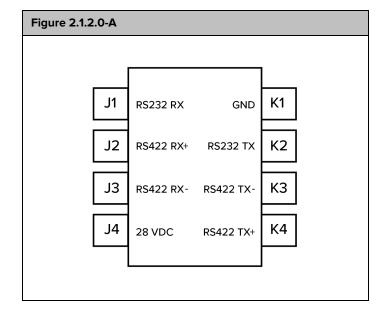

The NEXSYS ARINC 429 Signal Converter inputs are Power (28V), Ground (GND), Receive A (RXA) and Receive B (RXB). See additional sections for specific details concerning the Input/Output (I/O) interface. The inputs include the following characteristics for custom data conversion and output control. Input circuity is diode isolated, buffered, and debounced for reliable operation.

28V (PIN 4): Operating voltage (Nom.), 8 mA Current Draw (Max).

GND (PIN 5): Continuous Ground required, otherwise, inadvertent operation could occur.

**RXA (PIN 2), RXB (PIN 3):** Two-wire data Receive (RX) interface that autonomously receives the ARINC 429 unit of Transmission (TX).

**RXA, RXB Installation Notes:** The industry standard connection should include two wires that are twisted pairs with shielded ground cabling, which provides a balanced differential signal transmission. Multiple converters wire together, in parallel chain termination method, see Figure 2.1.1.0-B.

Note: ARINC 429 converters are tested to operate without twisted or shielding wires.

### **Standard ARINC 429 Configuration Options**

The NEXSYS ARINC 429 Signal Converters can be customized to provide an application-specific control interface to other avionics equipment. Standard

ARINC 429 data bus protocol and 32-bit word format options are configured, by utilizing the online Part Configurator.

**Label:** The specification of an octal (base-8) label (000-377). When energized, if a loss of data should occur, the converter latches the last valid transmission until valid data is once again received.

**Data Bit(s):** The specification of data bit (11-31) to be used as Discrete Outputs or to be used in Binary Outputs, see *Standard Output Characteristics*.

**Source/Destination Identifiers (SDI):** The specification to enable or disable (ignore) bits 9 and 10, used as an extension of the label for valid label identification.

**Transmission Speed:** The specification of the speed by which a converter receives (RX) the ARINC 429 unit of transmission (TX). The options are either High speed (100 kbps) or Low speed (12.5 kbps).

## Standard Output Characteristics

NEXSYS Signal Converters (SR429/1M, SR429/4M, and SR429/4D) receive (RX) an ARINC 429 data transmission (TX), which is decoded and converted into active discrete output(s). One or more single (unary) bits in the ARINC 429 data word can be converted into discrete outputs, depending upon the configuration type that is specified. The available configuration types provide up to three distinct output control activation options; Discrete Outputs, Decoded Outputs and the Failure Output.

All outputs are open-drain High-Z (Open) when not active. The output load capacity is 1.0 A for the SR429/1M and 0.5 A for SR429/4M and SR429/4D, see Figure 2.1.1.4-A (Operating Parameters) for electrical load rating types.

**Discrete Outputs:** Two Active Output options are available when converting the unary ARINC data bit to a Discrete Output: Standard, High-Z (Open) when Bit = 1 or Inverted, or Low (Ground) when Bit = 1. When Bit = 0 the output is orthogonal to the specified level when Bit = 1, see Figure 2.1.1.0-C.

| Figure 2.1.1.0-C |                     |                                   |  |  |  |

|------------------|---------------------|-----------------------------------|--|--|--|

| Output Option    | DATA BIT<br>(Value) | DISCRETE OUTPUT<br>(Signal Level) |  |  |  |

| Standard         | 1                   | High-Z (Open)                     |  |  |  |

| Stalldald        | 0                   | Low (Ground)                      |  |  |  |

| Inverted         | 1                   | Low (Ground)                      |  |  |  |

| inverted         | 0                   | High-Z (Open)                     |  |  |  |

ARINC 429 TXA

ARINC 429 TXB

SHIELDED

SR429

Signal

Converter

SR429

Signal

Converter

**Decoded Outputs** - Active Outputs can also represent the Binary Decode (BD) of multiple bits, and the Decoded Outputs options are: the BD variations of two or three data bits in the SR429/4D or of the Sign/Status Matrix bits (30, 31) available in the SR429/4M. Active Decoded Outputs are specified as Low (Ground) or High-Z (Open) when the decode = *TRUE*, see Figure 2.1.1.0-D.

Data bits that are specified for the BD function are positioned from MSB (Most Significant Bit) to LSB (Least Significant Bit). The MSB may also

| Figure 2.1.1.0-D        |                              |                                  |  |  |  |

|-------------------------|------------------------------|----------------------------------|--|--|--|

| Output Option           | BINARY DECODE<br>(Variation) | DECODED OUTPUT<br>(Signal Level) |  |  |  |

| Low (Ground) when       | BD = TRUE                    | Low (Ground)                     |  |  |  |

| Decode Variation = TRUE | BD = FALSE                   | High-Z (Open)                    |  |  |  |

| High-Z (Open) when      | BD = TRUE                    | High-Z (Open)                    |  |  |  |

| Decode Variation = TRUE | BD = FALSE                   | Low (Ground)                     |  |  |  |

function as the sign bit in the two's complement operation to represent a negative value (i.e., negative altitude, voltage, or temperature), with the addition of other NEXSYS components.

**Failure Output** - The NEXSYS ARINC 429 Signal Converter is also designed to monitor power and health of the internal IC receiver and offers two options for failure detection, Health and Watchdog, see <a href="Figure 2.1.1.0-E">Figure 2.1.1.0-E</a>. Both options monitor the internal IC and produce an Active Output upon failure of the receiver IC and/or failure to receive valid ARINC data within a specified time buffer. The Health option also monitors loss of unit power.

Health and Watchdog include a buffer-timer that is intended to monitor that valid data is received within a specified time. Health and Watchdog timing is specified during part number configuration, and the options are  $0.5 \, \text{s}$ ,  $1.0 \, \text{s}$ .  $1.75 \, \text{s}$ ,  $1.0 \, \text{s}$ ,  $1.0 \, \text{s}$ .  $1.0 \, \text{s}$ .

| Figure 2.1.1.0-E |                |                                  |  |  |

|------------------|----------------|----------------------------------|--|--|

| Output Option    | IC<br>(Status) | FAILURE OUTPUT<br>(Signal Level) |  |  |

| Health           | NORM           | Low (Ground)                     |  |  |

| Health           | FAIL           | High-Z (Open)                    |  |  |

| \\/_+_           | NORM           | High-Z (Open)                    |  |  |

| Watchdog         | FAIL           | Low (Ground)                     |  |  |

In the SR429/1M, only the Health version of the Failure Output is available which can be combined with additional external failure discretes to activate the Failure Output (FAIL, PIN 6), see "ARINC 429 Single-Bit Converter (SR429/1M)" on the facing page.

## 2.1.1.1 ARINC 429 Single-Bit Converter (SR429/1M)

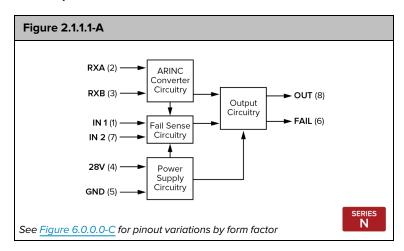

The ARINC 429 Single-Bit Converter (SR429/1M) is a Series N (8 Pin) device that offers one Discrete Output (OUT, PIN 8) from a single bit and one Failure Output (FAIL, PIN 6) that activates when the Fail Sense Circuitry detects a failure condition, see Figure 2.1.1.1-A. Output options are shown below in table Figure 2.1.1.1-B.

The FAIL output (FAIL, PIN 6) from the Fail Sense Circuitry is a Health Failure Output, defined as Normal = Low (Ground) and Fail = High-Z (Open). The primary purpose of the FAIL output is to monitor the power and health of the internal IC. The Fail Sense Circuitry can be bypassed if unused.

Optionally, the SR429/1M provides two (IN 1, PIN 1 and IN 2, PIN 7) independent failure inputs to the Fail Sense Circuitry that allows simultaneous monitoring of the internal IC health and signal level transitions from two external failure inputs. IN 1 and IN 2 are inputs with specific failure signal definitions.

- IN 1 (PIN 1): Triggers the FAIL output (PIN 6) upon a fixed input level transition from Normal = High, High-Z (Open) or > +20 VDC to Fail = Low (Ground) or < +6 VDC ( ). IN 1 may remain disconnected if unused.

- **IN 2 (PIN 7):** Triggers the FAIL output (PIN 6) upon one of two selectable input level transitions as described below ( $\searrow$ ). IN 2 must remain connected to the specified Normal signal level if unused.

- Normal = Low (Ground) or < +6 VDC to Fail = High, High-Z (Open) or > +20 VDC.

- Normal = High, High-Z (Open) or > +20 VDC to Fail = Low (Ground) or < +6 VDC (similar to IN 1).

When either IN 1 or IN 2 detects a signal level transition as defined above, or the internal IC has failed, the FAIL output transitions from Normal = Low (Ground) to Fail = High-Z (Open).

|          | Figure 2.1.1.1-B I/O OPTIONS                       |                                                                                                                                                          |  |  |

|----------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          | Pin 6 (FAIL)                                       | Pin 8 (OUT)                                                                                                                                              |  |  |

| SERIES N | н                                                  | 11 to 31                                                                                                                                                 |  |  |

|          | OPTION D                                           | DEFINITION                                                                                                                                               |  |  |

|          | H Failure Output (Health) is Fail = High-Z (Open). |                                                                                                                                                          |  |  |

|          | 11 to 31                                           | For a single-bit, 11 to 31 inclusive, Discrete Output can be specified as Standard = High-Z (Open) when Bit = 1 or Inverted = Low (Ground) when Bit = 1. |  |  |

## 2.1.1.2 ARINC 429 Multi-Bit Converter (SR429/4M)

The ARINC 429 Multi-Bit Converter (SR429/4M) is available as a NEXSYS Series N (8 Pin) or Series R (12 Pin) signal converter.

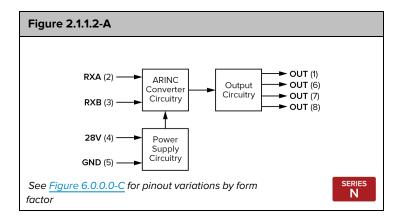

Series N (8 Pin) SR429/4M: Provides four

Discrete or Failure Outputs (PINS 1, 6-8), see

Figure 2.1.1.2-A. Discrete Outputs and Failure

Outputs can be repeated to avoid external

splicing. Output options for the four outputs

are shown in detail, see Figure 2.1.1.2-C.

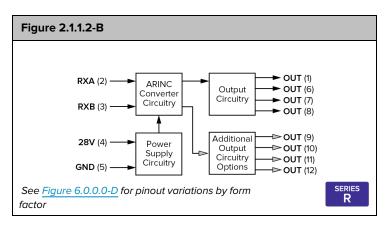

Series R (12 Pin) SR429/4M: Provides four Discrete or Failure Outputs (PINS 1, 6-8) plus four additional outputs (PINS 9-12), see Figure 2.1.1.2-B. Discrete Outputs and Failure Outputs can be repeated to avoid external splicing. The additional outputs (PINS 9-12) can be used as Decoded Outputs of the Sign/Status Matrix (SSM) bits 30 and 31 or as additional Discrete or Failure Outputs. When additional Discrete Outputs are specified, the signal levels will be the inverted value of the initial four Discrete Outputs. Output options, including the ability to repurpose SSM decode variation 00 (PIN 9) with additional data, are shown in detail in, see Figure 2.1.1.2-C.

| Figure 2.1.1.2-C I/O OPTIONS                                                                                                                                                                                                                                    |                                       |                                      |                                                                                                    |                                                                                                                   |                                                                                                                                              |                     |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|

| PIN 6                                                                                                                                                                                                                                                           | PIN 7                                 | PIN 8                                | PIN 9                                                                                              | PIN 10                                                                                                            | PIN 11                                                                                                                                       | PIN 12              |  |

| r W 11 to 31, H or W                                                                                                                                                                                                                                            | 11-31, H or W                         | 11 to 31, H or W                     | -                                                                                                  | -                                                                                                                 | -                                                                                                                                            | -                   |  |

| r W 11 to 31, H or W                                                                                                                                                                                                                                            | 11 to 31, H or W                      | 11 to 31                             | [9]                                                                                                | [10] or H                                                                                                         | [11] or H                                                                                                                                    | [12] or H           |  |

| r W 11 to 31, H or W                                                                                                                                                                                                                                            | 11 to 31, H or W                      | H or W                               | H or W                                                                                             | [10] or H                                                                                                         | [11] or H                                                                                                                                    | [12] or H           |  |

| r W 11 to 31, H or W                                                                                                                                                                                                                                            | 11 to 31, H or W                      | 11 to 29                             | H or W                                                                                             | [10] or H                                                                                                         | [11] or H                                                                                                                                    | [12] or H           |  |

| 11 to 29                                                                                                                                                                                                                                                        | 11 to 29                              | 11 to 31, H or W                     | SSM00                                                                                              | SSM01                                                                                                             | SSM10                                                                                                                                        | SSM11               |  |

| 11 to 29                                                                                                                                                                                                                                                        | 11 to 29                              | 11 to 31, H or W                     | H or W                                                                                             | SSM01                                                                                                             | SSM10                                                                                                                                        | SSM11               |  |

| 11 to 29                                                                                                                                                                                                                                                        | 11 to 29                              | 11 to 31                             | [9]                                                                                                | SSM01                                                                                                             | SSM10                                                                                                                                        | SSM11               |  |

| 11 to 29                                                                                                                                                                                                                                                        | 11 to 29                              | H or W                               | H or W                                                                                             | SSM01                                                                                                             | SSM10                                                                                                                                        | SSM11               |  |

|                                                                                                                                                                                                                                                                 | OPTION DEFINITION                     |                                      |                                                                                                    |                                                                                                                   |                                                                                                                                              |                     |  |

| For a single bit, 11 to 29 or 11 to 31 inclusive, Discrete Output can be specified as Standard = High-Z (Open) when Bit = 1 o Inverted = Low (Ground) when Bit = 1.                                                                                             |                                       |                                      |                                                                                                    |                                                                                                                   | when Bit = 1 or                                                                                                                              |                     |  |

| H Failure Output is High-Z (Open) when Health Monitor = Fail.                                                                                                                                                                                                   |                                       |                                      |                                                                                                    |                                                                                                                   |                                                                                                                                              |                     |  |

| Failure Output is Low (Ground) when Watchdog = Fail.                                                                                                                                                                                                            |                                       |                                      |                                                                                                    |                                                                                                                   |                                                                                                                                              |                     |  |

| Will be the same Bit specified on PIN 8, Discrete Output can be specified as Standard = High-Z (Open) when Bit = 1 or Inverted = Low (Ground) when Bit = 1 regardless of output selection for PIN 8.                                                            |                                       |                                      |                                                                                                    |                                                                                                                   |                                                                                                                                              |                     |  |

| [10] Will be the same Bit specified on PIN 7, Discrete Output is Inverted = Low (Ground) regardless of output selection for PI 7.  Will be the same Bit specified on PIN 6, Discrete Output is Inverted = Low (Ground) regardless of output selection for PI 6. |                                       |                                      |                                                                                                    |                                                                                                                   | lless of output se                                                                                                                           | lection for PIN     |  |

|                                                                                                                                                                                                                                                                 |                                       |                                      |                                                                                                    |                                                                                                                   | election for PIN                                                                                                                             |                     |  |

| Will be the same                                                                                                                                                                                                                                                | Bit specified on PIN                  | 1, Discrete Output                   | is Inverted = Low                                                                                  | (Ground) regard                                                                                                   | less of output se                                                                                                                            | lection for PIN 1   |  |

| 1 '                                                                                                                                                                                                                                                             | •                                     |                                      | outs can be specif                                                                                 | fied as High-Z (O                                                                                                 | pen) when DECC                                                                                                                               | DE = <i>TRUE</i> or |  |

|                                                                                                                                                                                                                                                                 | Binary Decode of<br>Inverted = Low (G | Binary Decode of SSM Bits (Bits 30 a | Binary Decode of SSM Bits (Bits 30 and 31), Binary Outpliverted = Low (Ground) when DECODE = TRUE. | Binary Decode of SSM Bits (Bits 30 and 31), Binary Outputs can be specificated = Low (Ground) when DECODE = TRUE. | Binary Decode of SSM Bits (Bits 30 and 31), Binary Outputs can be specified as High-Z (O Inverted = Low (Ground) when DECODE = <i>TRUE</i> . | ··                  |  |

## 2.1.1.3 ARINC 429 Multi-Bit Decoding Converter (SR429/4D)

The ARINC 429 Multi-Bit Decoding Converter (SR429/4D) is available as a NEXSYS Series N (8 Pin) or Series R (12 Pin) component.

The SR429/4D can be configured in two standard types of decoding:

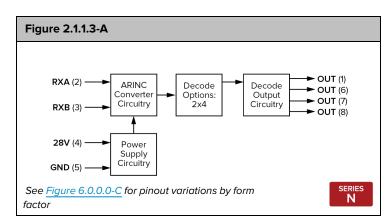

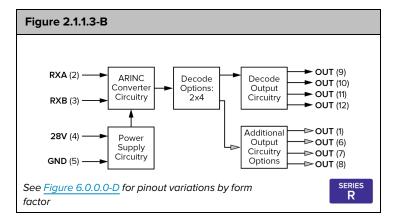

- 2 x 4 Decoder: Performs a Binary Decode (BD) of two ARINC data bits producing four Decoded Outputs. The 2 X 4 Decoding Converter can be configured as a Series N (8 Pin) device, see <u>Figure 2.1.1.3-A</u> or a Series R (12 Pin) device with additional outputs, see <u>Figure 2.1.1.3-B</u>.

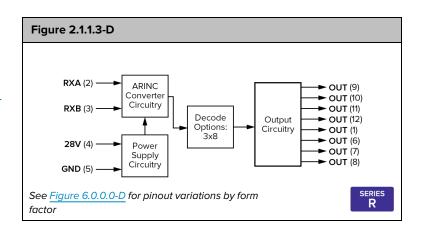

- **3 x 8 Decoder:** Performs a Binary Decode (BD) of three ARINC data bits producing eight Decoded Outputs. The 3 X 8 Decoding Converter is configured as a Series R (12 Pin) device, see <u>Figure 2.1.1.3-D</u>. BD variations 000 and/or 111 can be repurposed as Discrete or Failure Outputs.

#### SR429/4D with 2 x 4 Decoder

- Series N (8 Pin) 2 x 4 Decoder: Four Decoded Outputs (PINS 1, 6-8); each output is a Binary Decode (BD) variation (00, 01, 10, 11) of two bits according to the ARINC 429 word protocol, see <u>Figure 2.1.1.3-A</u>. Output options include the ability to repurpose the BD variation 00 (PIN 1) and/or the BD variation 11 (PIN 8) with additional data, see <u>Figure 2.1.1.3-C</u>.

- Series R (12 Pin) 2 x 4 Decoder: Eight total outputs. Four Decoded Outputs (PINS 9-12); each output is a Binary Decode (BD) variation (00, 01, 10, 11) of two bits according to the ARINC 429 word protocol, see Figure 2.1.1.3-B. Additional output options include the ability to repurpose the BD variation 00 (PIN 9) and/or the BD variation 11 (PIN 12) with additional data. Four additional outputs (PIN 1, 6-8) are available for Discrete or Failure Outputs, see Figure 2.1.1.3-C for detail of the output options for all Series R pins.

|         | PIN 1                                                                                                                                                                                                                                                                                                                                                                                                        | PIN 6                                                                                                                                                               | PIN 7                   | PIN 8                 | PIN 9            | PIN 10              | PIN 11            | PIN 12        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|------------------|---------------------|-------------------|---------------|

|         | DEC00                                                                                                                                                                                                                                                                                                                                                                                                        | DEC01                                                                                                                                                               | DEC10                   | DEC11                 | -                | -                   | -                 | -             |

| Z<br>S: | 11 to 29                                                                                                                                                                                                                                                                                                                                                                                                     | DEC01                                                                                                                                                               | DEC10                   | DEC11                 | -                | -                   | -                 | -             |

| SERIES  | DEC00                                                                                                                                                                                                                                                                                                                                                                                                        | DEC01                                                                                                                                                               | DEC10                   | 11 to 31, H or W      | -                | -                   | -                 | -             |

| 0)      | 11 to 29                                                                                                                                                                                                                                                                                                                                                                                                     | DEC01                                                                                                                                                               | DEC10                   | 11 to 31, H or W      | -                | -                   | -                 | -             |

|         | 11 to 29                                                                                                                                                                                                                                                                                                                                                                                                     | MSB (11 to 31, H,<br>W)                                                                                                                                             | LSB (11 to 31, H,<br>W) | 11 to 31, H or W      | DEC00            | DEC01               | DEC10             | DEC11         |

| ES R    | 11 to 29                                                                                                                                                                                                                                                                                                                                                                                                     | MSB (11 to 31, H,<br>W)                                                                                                                                             | LSB (11 to 31, H,<br>W) | 11 to 31              | [9]              | DEC01               | DEC10             | DEC11         |

| SERIES  | 11 to 29                                                                                                                                                                                                                                                                                                                                                                                                     | MSB (11 to 31, H,<br>W)                                                                                                                                             | LSB (11 to 31, H,<br>W) | H or W                | H or W           | DEC01               | DEC10             | DEC11         |

|         | 11 to 29                                                                                                                                                                                                                                                                                                                                                                                                     | MSB (11 to 31, H,<br>W)                                                                                                                                             | LSB (11 to 31, H,<br>W) | 11 to 29              | H or W           | DEC01               | DEC10             | DEC11         |

|         |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                     |                         | OPTION DEFI           | NOITION          |                     |                   |               |

|         | DEC00 to<br>DEC11                                                                                                                                                                                                                                                                                                                                                                                            | Binary decode var<br>when DECODE = 7                                                                                                                                | riations for specifie   | d label and bits; Bii | nary Outputs car | n be specified as I | Low (Ground) or I | High-Z (Open) |

|         | 11 to 29, 11 to 31                                                                                                                                                                                                                                                                                                                                                                                           | For a single bit, 11 to 29 or 11 to 31 inclusive, Discrete Output can be specified as Standard = High-Z (Open) when Bit = 1 o Inverted = Low (Ground) when Bit = 1. |                         |                       |                  |                     |                   |               |

|         | Н                                                                                                                                                                                                                                                                                                                                                                                                            | Failure Output is H                                                                                                                                                 | ligh-Z (Open) wher      | Health Monitor =      | Fail.            |                     |                   |               |

|         | W Failure Output is Low (Ground) when Watchdog = Fail.                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                     |                         |                       |                  |                     |                   |               |

|         | [9] Must be the same Bit specified on PIN 8, Discrete Output can be specified as Standard = High-Z (Open) when Bit = 1 or Inverted = Low (Ground) when Bit = 1 regardless of output selection for PIN 8.  MSB, LSB  Discrete Output of Most/Least significant bit used in 2 x 4 decoder. Discrete Outputs can be specified as Standard = High-Z (Open) when Bit = 1 or Inverted = Low (Ground) when Bit = 1. |                                                                                                                                                                     |                         |                       |                  | hen Bit = 1 or      |                   |               |

|         |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                     |                         |                       |                  | Standard = Hig      |                   |               |

#### SR429/4D with 3X8 Decoder

• Series R (12 Pin) 3 x 8 Decoder: Eight Binary Outputs (PINS 1, 6-12); each output is a Binary Decode (BD) variation (000, 001, 010, 011, 100, 101, 110, 111) of three bits according to the ARINC 429 word protocol, see Figure 2.1.1.3-D. Output options include the ability to repurpose the BD variation 000 (PIN 9) and/or the BD variation 111 (PIN 8) with additional data, see Figure 2.1.1.3-E.

|        | Figure 2.1.1.3-E I/O OPTIONS                           |                                                                                                                                                                                                      |                                                                                                                                                                      |                    |                   |                    |                  |                  |  |

|--------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|--------------------|------------------|------------------|--|

|        | PIN 9                                                  | PIN 10                                                                                                                                                                                               | PIN 11                                                                                                                                                               | PIN 12             | PIN 1             | PIN 6              | PIN 7            | PIN 8            |  |

|        | DEC000                                                 | DEC001                                                                                                                                                                                               | DEC010                                                                                                                                                               | DEC011             | DEC100            | DEC101             | DEC110           | DEC111           |  |

|        | 11 to 31, H or W                                       | DEC001                                                                                                                                                                                               | DEC010                                                                                                                                                               | DEC011             | DEC100            | DEC101             | DEC110           | DEC111           |  |

|        | DEC000                                                 | DEC001                                                                                                                                                                                               | DEC010                                                                                                                                                               | DEC011             | DEC100            | DEC101             | DEC110           | 11 to 31, H or V |  |

| ES R   | [9]                                                    | DEC001                                                                                                                                                                                               | DEC010                                                                                                                                                               | DEC011             | DEC100            | DEC101             | DEC110           | 11 to 31         |  |

| SERIES | H or W                                                 | DEC001                                                                                                                                                                                               | DEC010                                                                                                                                                               | DEC011             | DEC100            | DEC101             | DEC110           | 11 to 29, H or V |  |

|        | DEC000                                                 | DEC001                                                                                                                                                                                               | DEC010                                                                                                                                                               | DEC011             | DEC100            | DEC101             | DEC110           | DEC111           |  |

|        | 11 to 31, H or W                                       | DEC001                                                                                                                                                                                               | DEC010                                                                                                                                                               | DEC011             | DEC100            | DEC101             | DEC110           | DEC111           |  |

|        | DEC000                                                 | DEC001                                                                                                                                                                                               | DEC010                                                                                                                                                               | DEC011             | DEC100            | DEC101             | DEC110           | 11 to 31, H or V |  |

|        | OPTION DEFINITION                                      |                                                                                                                                                                                                      |                                                                                                                                                                      |                    |                   |                    |                  |                  |  |

|        | DEC000 to<br>DEC111                                    | Binary decode var<br>when DECODE = 3                                                                                                                                                                 | •                                                                                                                                                                    | ed label and bits; | Binary Outputs ca | an be specified as | s Low (Ground) o | r High-Z (Open)  |  |

|        | 11 to 29, 11 to 31                                     | ,                                                                                                                                                                                                    | For a single bit, 11 to 29 or 11 to 31 inclusive, Discrete Output can be specified as Standard = High-Z (Open) when Bit = 1 or Inverted = Low (Ground) when Bit = 1. |                    |                   |                    |                  |                  |  |

|        | Н                                                      | Failure Output is H                                                                                                                                                                                  | ligh-Z (Open) whe                                                                                                                                                    | n Health Monito    | r = Fail.         |                    |                  |                  |  |

|        | W Failure Output is Low (Ground) when Watchdog = Fail. |                                                                                                                                                                                                      |                                                                                                                                                                      |                    |                   |                    |                  |                  |  |

|        | [9]                                                    | Must be the same Bit specified on PIN 8, Discrete Output can be specified as Standard = High-Z (Open) when Bit = 1 or Inverted = Low (Ground) when Bit = 1 regardless of output selection for PIN 8. |                                                                                                                                                                      |                    |                   |                    |                  |                  |  |

## **2.1.1.4 ARINC 429 Signal Converters, Operating Parameters**

| Figure 2.1.1.4-A                                                                | -                                                                                                                                                          |  |  |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Description                                                                     | Parameters                                                                                                                                                 |  |  |

| Operatin                                                                        | g Parameters                                                                                                                                               |  |  |

| Operating Voltage (Max./Nom./ Min.)                                             | +32 VDC /+28 VDC/+18 VDC                                                                                                                                   |  |  |

| Power Supply Input Current                                                      | 8 mA (Maximum)                                                                                                                                             |  |  |

| Reset Time from Power Loss at 25°C                                              | 5 sec (Minimum)                                                                                                                                            |  |  |

| Hold Up Time from Power Loss at 25°C                                            | 200 ms (Minimum)                                                                                                                                           |  |  |

| Input F                                                                         | Parameters                                                                                                                                                 |  |  |

| IN 1, IN 2 (SR429/1M) Input Timing at 25°C                                      | 5 ms (Typical)                                                                                                                                             |  |  |

| IN 1, IN2 <b>(SR429/1M)</b> Low Level Input Current (I <sub>IL</sub> ) at 25°C  | 1 mA (Maximum)                                                                                                                                             |  |  |

| $^{*}$ IN 1, IN 2 (SR429/1M) Low Level Input Voltage (V <sub>IL</sub> ) at 25°C | <+6 VDC                                                                                                                                                    |  |  |

| * High <b>(SR429/1M)</b> Level Input Voltage (V <sub>IH</sub> ) at 25°C         | >+20 VDC                                                                                                                                                   |  |  |

| ARINC 429 Inputs (SR429/1M, SR429/4M, SR429/4D)                                 | IAW ARINC 429 Protocol                                                                                                                                     |  |  |

| IN 1, IN 2 inputs                                                               | s are diode isolated                                                                                                                                       |  |  |

| Output                                                                          | Parameters                                                                                                                                                 |  |  |

| Output Load Capacity                                                            | SR429/1M: Fused MOSFET - 1.0 A (Resistive),<br>0.5 A (Motor/Inductive/Lamp)<br>SR429/4M, SR429/4D: IntelliFET® 0.5 A<br>(Resistive/Motor/Inductive/Lamp)   |  |  |

| On-State Resistance at 25°C                                                     | <b>SR429/1M:</b> Typical 0.07 ohms / Maximum 0.09 ohms <b>SR429/4M, SR429/4D:</b> Typical 0.4 ohms / Maximum 0.6 ohm                                       |  |  |

| Off-State Resistance at 25°C                                                    | SR429/1M: Open Drain (High-Z), Fuse-Protected MOSFET, +32 VDC Maximum SR429/4M, SR429/4D: Open Drain (High-Z), Self-Protected IntelliFET®, +32 VDC Maximum |  |  |

| Tem                                                                             | perature                                                                                                                                                   |  |  |

| Operating Temperature                                                           | -55°C to +85°C                                                                                                                                             |  |  |

| Non-Operating Temperature                                                       | -55°C to +125°C                                                                                                                                            |  |  |

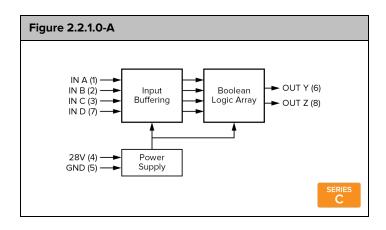

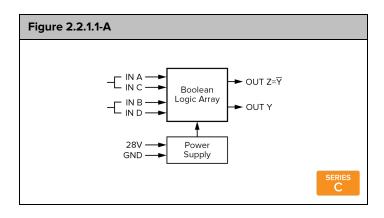

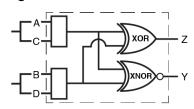

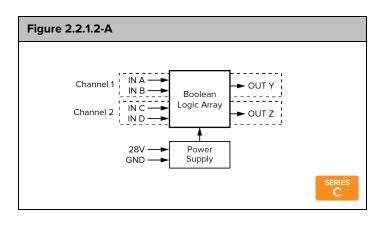

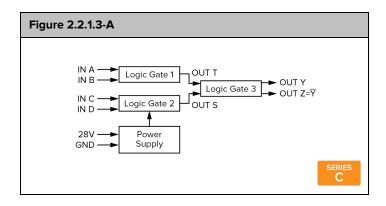

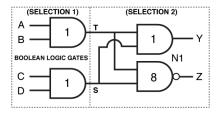

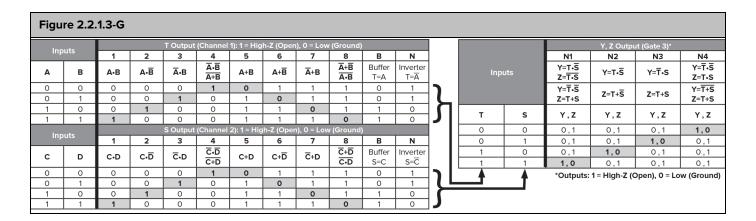

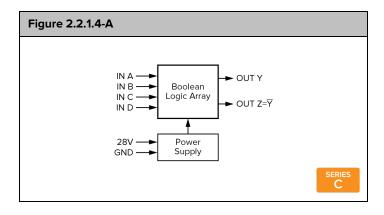

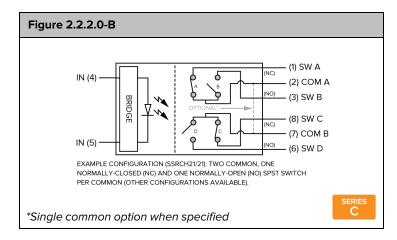

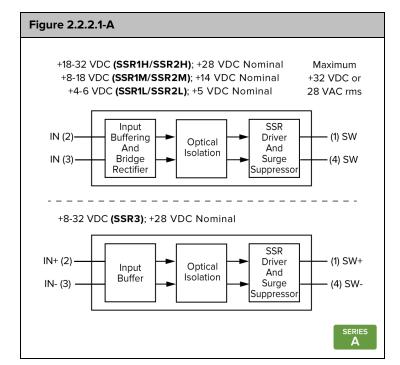

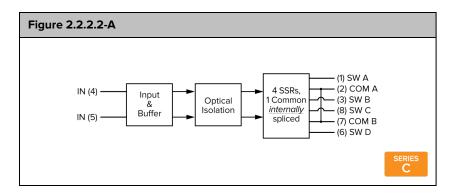

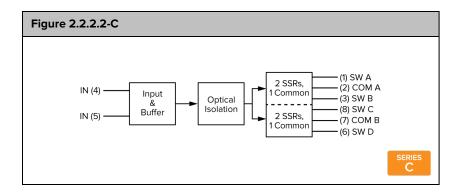

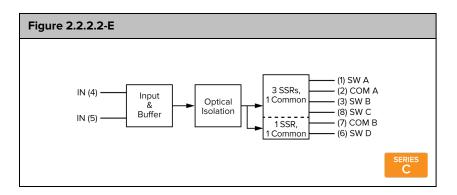

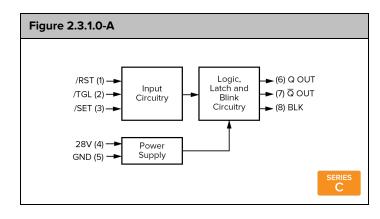

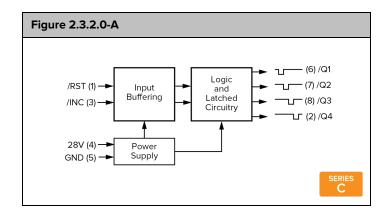

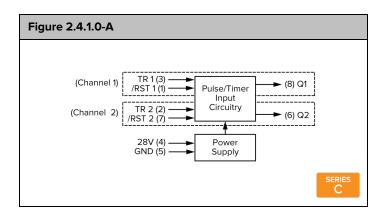

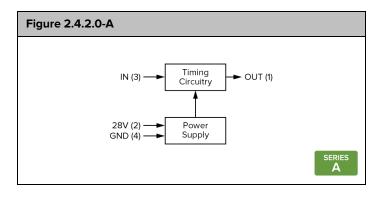

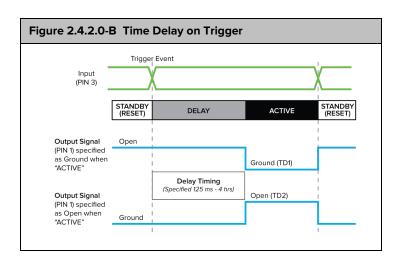

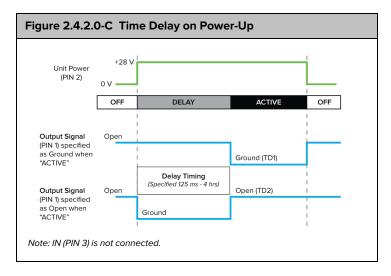

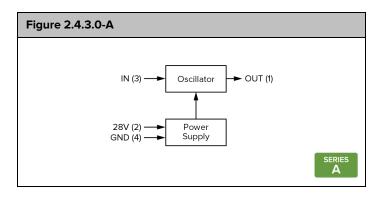

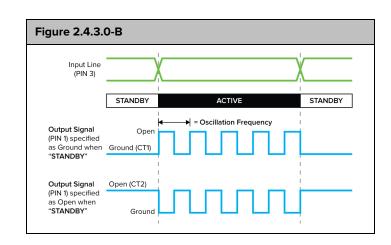

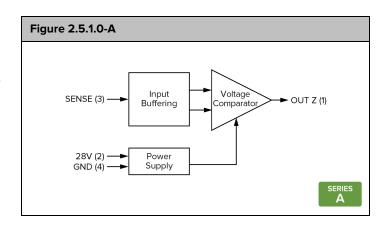

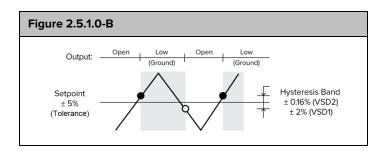

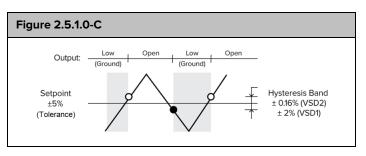

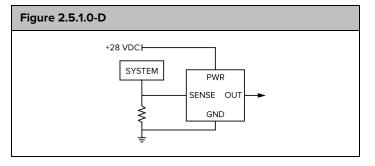

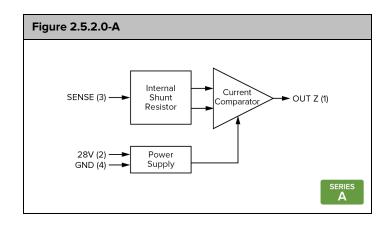

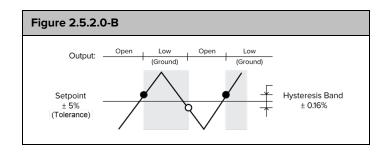

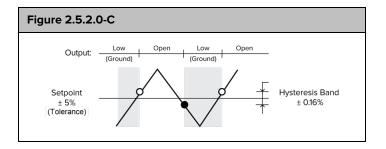

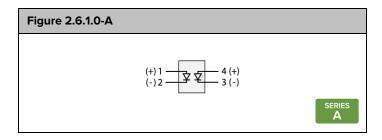

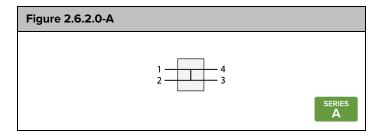

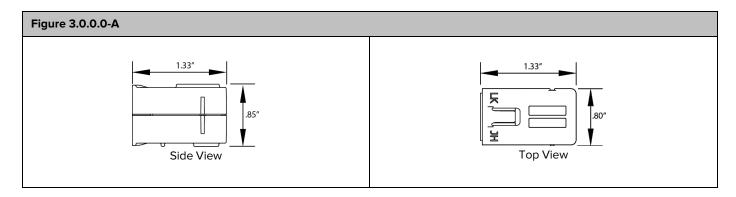

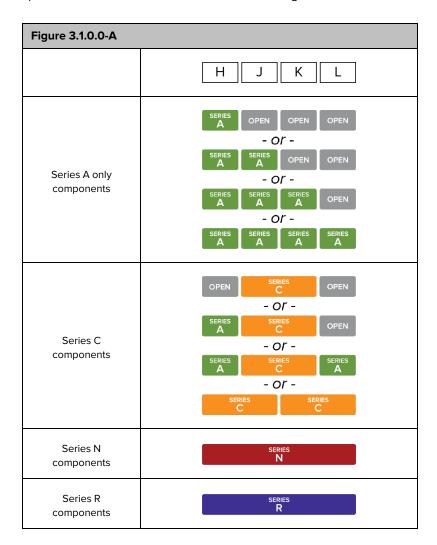

|                                                                                 | liability<br>-217F, Notice 2                                                                                                                               |  |  |